## AN8049FHN

# 1.8-volt 3-channel step-up, step-down, and polarity inverting DC-DC converter control IC

### Overview

The AN8049FHN is a three-channel PWM DC-DC converter control IC that features low-voltage operation. This IC can form a power supply that provides two stepup outputs and one step-down or polarity inverted output with a minimal number of external components. Minimal operating supply voltage of this IC is as low as 1.8 V, so that it can operate from 2 dry-batteries.

#### Features

- Wide operating supply voltage range: 1.8 V to 14 V

- High-precision reference voltage circuit

- V<sub>REF</sub> pin voltage: ±1%

- Error amplifier: ±1.5%

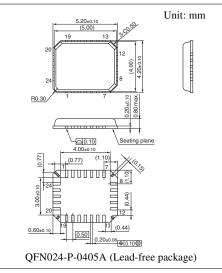

- Ultrathin surface mounting package for miniaturized and thinner power supplies

- Supports control over a wide output frequency range: 20 kHz to 1 MHz

- On/off (sequence control) pins provided for each channel for easy sequence control setup

- The negative supply error amplifier supports 0-volt input. Common-mode input voltage range: -0.1 V to V<sub>CC</sub> -1.4 V

- This allows the number of external components to be reduced by two resistors.

- Fixed duty factor: 86%

However, the duty can be adjusted to anywhere from 0% to 100% with an external resistor.

- Timer latch short-circuit protection circuit (charge current: 1.1 µA typical)

- Low input voltage malfunction prevention circuit (U.V.L.O.)

- (operation start voltage: 1.67 V typical)

- Standby function (active-high control input, standby mode current:  $1 \,\mu A$  maximum)

#### Applications

• Electronic equipment that requires a power supply system

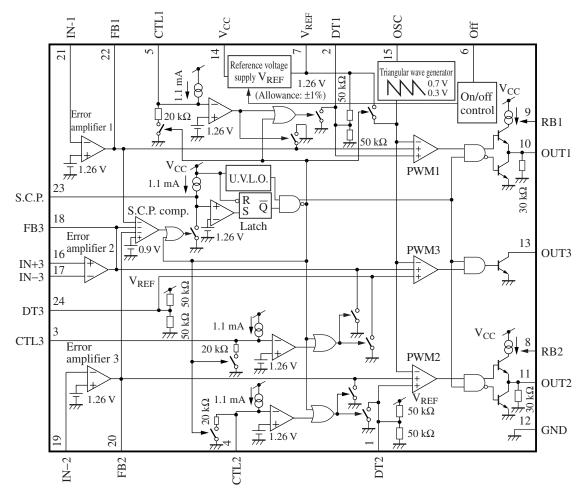

#### Block Diagram

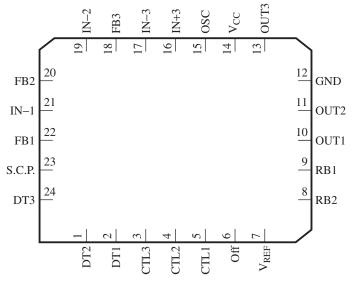

#### Pin Descriptions

| Pin No. | Description      | Pin No. | Description     |

|---------|------------------|---------|-----------------|

| 1       | DT2              | 13      | OUT3            |

| 2       | DT1              | 14      | V <sub>CC</sub> |

| 3       | CTL3             | 15      | OSC             |

| 4       | CTL2             | 16      | IN+3            |

| 5       | CTL1             | 17      | IN-3            |

| 6       | Off              | 18      | FB3             |

| 7       | V <sub>REF</sub> | 19      | IN-2            |

| 8       | RB2              | 20      | FB2             |

| 9       | RB1              | 21      | IN-1            |

| 10      | OUT1             | 22      | FB1             |

| 11      | OUT2             | 23      | S.C.P.          |

| 12      | GND              | 24      | DT3             |

#### ■ Absolute Maximum Ratings

| Parameter                                              | Symbol               | Rating          | Unit |

|--------------------------------------------------------|----------------------|-----------------|------|

| Supply voltage                                         | V <sub>CC</sub>      | 14.2            | V    |

| Off pin allowable application voltage                  | V <sub>OFF</sub>     | 14.2            | V    |

| Error amplifier input allowable application voltage *2 | V <sub>IN</sub>      | V <sub>CC</sub> | V    |

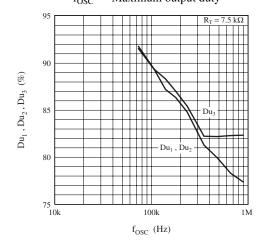

| OUT1 and OUT2 pin output source current                | I <sub>SO(OUT)</sub> | -50             | mA   |

| OUT3 pin output current                                | I <sub>SI(OUT)</sub> | +50             | mA   |

| Power dissipation *1                                   | P <sub>D</sub>       | 111             | mW   |

| Operating temperature                                  | T <sub>opr</sub>     | -30 to +85      | °C   |

| Storage temperature                                    | T <sub>stg</sub>     | -55 to +150     | °C   |

Note) \*1:  $T_a = 85^{\circ}C$ . For the independent IC without a heat sink.

\*2: When  $V_{CC}$  is less than 6 V,  $V_{IN\!-\!1}$  and  $V_{IN\!+\!2}$  must be  $V_{CC}$  .

### Recommended Operating Range

| Parameter                                                  | Symbol               | Range        | Unit |

|------------------------------------------------------------|----------------------|--------------|------|

| Off pin application voltage                                | V <sub>OFF</sub>     | 0 to 14      | V    |

| OUT1 and OUT2 pin output source current                    | I <sub>SO(OUT)</sub> | -40 (min.)   | mA   |

| OUT3 pin output current                                    | I <sub>SI(OUT)</sub> | 40 (max.)    | mA   |

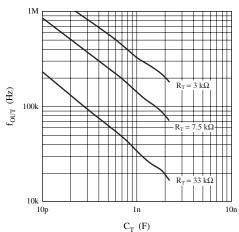

| Timing resistance                                          | R <sub>T</sub>       | 3 to 33      | kW   |

| Timing capacitance                                         | C <sub>T</sub>       | 100 to 1000  | pF   |

| Oscillator frequency                                       | f <sub>OUT</sub>     | 20 to 1 000  | kHz  |

| Short-circuit protection time-constant setting capacitance | C <sub>SCP</sub>     | 1000 (min.)  | pF   |

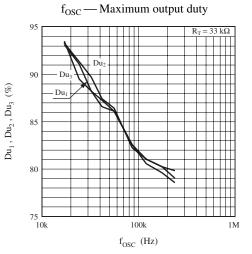

| Output current setting resistance                          | R <sub>B</sub>       | 750 to 15000 | Ω    |

## $\blacksquare$ Electrical Characteristics at V\_{CC} = 2.4 V, C\_{REF} = 0.1 $\mu F,\,T_a$ = 25°C

| Parameter                                     | Symbol               | Conditions                                    | Min   | Тур   | Max                     | Unit |

|-----------------------------------------------|----------------------|-----------------------------------------------|-------|-------|-------------------------|------|

| Reference voltage block                       |                      |                                               |       |       |                         |      |

| Reference voltage                             | V <sub>REF</sub>     | $I_{\text{REF}} = -0.1 \text{ mA}$            | 1.247 | 1.26  | 1.273                   | V    |

| Line regulation with input fluctuation        | Line                 | $V_{CC} = 1.8 V$ to 14 V                      | _     | 2     | 20                      | mV   |

| Load regulation                               | Load                 | $I_{REF} = -0.1 \text{ mA to } -1 \text{ mA}$ | -20   | -3    |                         | mV   |

| V <sub>REF</sub> temperature characteristics  | V <sub>RFEdT</sub>   | $T_a = -30^{\circ}C$ to $+85^{\circ}C$        | _     | 1     |                         | %    |

| V <sub>REF</sub> pin short-circuit current    | I <sub>OC</sub>      |                                               | —     | -10   |                         | mA   |

| U.V.L.O. block                                |                      |                                               |       |       |                         |      |

| Circuit operation start voltage               | V <sub>UON</sub>     |                                               | 1.59  | 1.67  | 1.75                    | V    |

| Error amplifier 1 block                       |                      |                                               |       |       |                         |      |

| Input threshold voltage 1                     | $V_{TH1}$            |                                               | 1.241 | 1.26  | 1.279                   | V    |

| Input bias current 1                          | I <sub>B1</sub>      |                                               |       | 0.1   | 0.2                     | μΑ   |

| High-level output voltage 1                   | $V_{\rm EH1}$        |                                               | 1.0   | 1.2   | 1.4                     | V    |

| Low-level output voltage 1                    | $V_{EL1}$            |                                               |       | _     | 0.2                     |      |

| Output source current 1                       | I <sub>SO(FB)1</sub> |                                               | -38   | -31   | -24                     | μΑ   |

| Output sink current 1                         | I <sub>SI(FB)1</sub> |                                               | 0.5   |       |                         | mA   |

| V <sub>TH</sub> temperature characteristics 1 | $V_{THdT1}$          | $T_a = -30^{\circ}C$ to $+85^{\circ}C$        |       | 1.5   |                         | %    |

| Open-loop gain 1                              | $A_{V1}$             |                                               |       | 80    | _                       | dB   |

| Error amplifier 2 block                       |                      |                                               |       |       |                         |      |

| Input threshold voltage 2                     | $V_{TH2}$            |                                               | 1.241 | 1.26  | 1.279                   | V    |

| Input bias current 2                          | I <sub>B2</sub>      |                                               | _     | 0.1   | 0.2                     | μΑ   |

| High-level output voltage 2                   | $V_{EH2}$            |                                               | 1.0   | 1.2   | 1.4                     | V    |

| Low-level output voltage 2                    | V <sub>EL2</sub>     |                                               | _     |       | 0.2                     |      |

| Output source current 2                       | I <sub>SO(FB)2</sub> |                                               | -38   | -31   | -24                     | μΑ   |

| Output sink current 2                         | I <sub>SI(FB)2</sub> |                                               | 0.5   |       |                         | mA   |

| V <sub>TH</sub> temperature characteristics 2 | V <sub>THdT2</sub>   | $T_a = -30^{\circ}C$ to $+85^{\circ}C$        |       | 1.5   |                         | %    |

| Open-loop gain 2                              | A <sub>V2</sub>      |                                               | _     | 80    |                         | dB   |

| Error amplifier 3 block                       |                      |                                               |       |       |                         |      |

| Input offset voltage                          | V <sub>IO</sub>      |                                               | -6    |       | 6                       | mV   |

| Common-mode input voltage range               | V <sub>ICR</sub>     |                                               | - 0.1 |       | V <sub>CC</sub><br>-1.4 | V    |

| Input bias current 3                          | I <sub>B3</sub>      |                                               | - 0.6 | - 0.3 | _                       | μΑ   |

| High-level output voltage 3                   | V <sub>EH3</sub>     |                                               | 1.0   | 1.2   | 1.4                     | V    |

| Low-level output voltage 3                    | V <sub>EL3</sub>     |                                               |       | _     | 0.2                     |      |

| Output source current 3                       | I <sub>SO(FB)3</sub> |                                               | -38   | -31   | -24                     | μA   |

| Output sink current 3                         | I <sub>SI(FB)3</sub> |                                               | 0.5   |       | _                       | mA   |

| Open-loop gain 3                              | A <sub>V3</sub>      |                                               |       | 80    |                         | dB   |

## Electrical Characteristics at V<sub>CC</sub> = 2.4 V, C<sub>REF</sub> = 0.1 $\mu$ F, T<sub>a</sub> = 25°C (continued)

| Parameter                                | Symbol                | Conditions                                                    | Min                | Тур  | Мах  | Unit |

|------------------------------------------|-----------------------|---------------------------------------------------------------|--------------------|------|------|------|

| Oscillator block                         |                       |                                                               |                    |      |      |      |

| Oscillator frequency                     | f <sub>OUT</sub>      | $R_T = 7.5 \text{ k}\Omega, C_T = 680 \text{ pF}$             | 170                | 190  | 210  | kHz  |

| Frequency supply voltage characteristics | $f_{\text{DV}}$       | $R_{\rm T} = 7.5 \text{ k}\Omega, C_{\rm T} = 680 \text{ pF}$ | _                  | 1    |      | %    |

| Frequency temperature characteristics    | f <sub>DT</sub>       | $R_{\rm T} = 7.5 \text{ k}\Omega, C_{\rm T} = 680 \text{ pF}$ | —                  | 3    |      | %    |

| Output 1 block                           |                       |                                                               |                    |      |      |      |

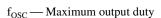

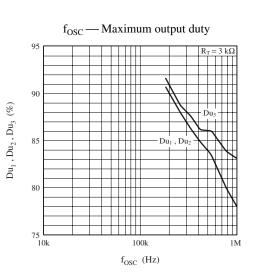

| Output duty factor 1                     | Du <sub>1</sub>       | $R_{T} = 7.5 \text{ k}\Omega, C_{T} = 680 \text{ pF}$         | 80                 | 86   | 92   | %    |

| High-level output voltage 1              | V <sub>OH1</sub>      | $I_0 = -10 \text{ mA}, R_B = 1 \text{ k}\Omega$               | $V_{CC}-1$         |      |      | V    |

| Low-level output voltage 1               | V <sub>OL1</sub>      | $I_0 = 10 \text{ mA}, R_B = 1 \text{ k}\Omega$                |                    |      | 0.2  | V    |

| Output source current 1                  | I <sub>SO(OUT)1</sub> | $V_0 = 0.7 \text{ V}, R_B = 1 \text{ k}\Omega$                | -32                | -27  | -22  | mA   |

| Output sink current 1                    | I <sub>SI(OUT)1</sub> | $V_0 = 0.7 \text{ V}, R_B = 1 \text{ k}\Omega$                | 40                 |      |      | mA   |

| Pull-down resistor 1                     | R <sub>O1</sub>       |                                                               | 20                 | 30   | 40   | kΩ   |

| Output 2 block                           |                       |                                                               |                    |      | ·    |      |

| Output duty factor 2                     | Du <sub>2</sub>       | $R_T = 7.5 \text{ k}\Omega, C_T = 680 \text{ pF}$             | 80                 | 86   | 92   | %    |

| High-level output voltage 2              | V <sub>OH2</sub>      | $I_0 = -10 \text{ mA}, R_B = 1 \text{ k}\Omega$               | V <sub>CC</sub> -1 |      |      | V    |

| Low-level output voltage 2               | V <sub>OL2</sub>      | $I_0 = 10 \text{ mA}, R_B = 1 \text{ k}\Omega$                |                    |      | 0.2  | V    |

| Output source current 2                  | I <sub>SO(OUT)2</sub> | $V_0 = 0.7 V, R_B = 1 k\Omega$                                | -32                | -27  | -22  | mA   |

| Output sink current 2                    | I <sub>SI(OUT)2</sub> | $V_0 = 0.7 \text{ V}, R_B = 1 \text{ k}\Omega$                | 40                 |      |      | mA   |

| Pull-down resistor 2                     | R <sub>O2</sub>       |                                                               | 20                 | 30   | 40   | kΩ   |

| Output 3 block                           |                       |                                                               |                    |      |      |      |

| Output duty factor 3                     | Du <sub>3</sub>       | $R_{\rm T} = 7.5 \text{ k}\Omega, C_{\rm T} = 680 \text{ pF}$ | 80                 | 86   | 92   | %    |

| Output saturation voltage                | V <sub>O(SAT)</sub>   |                                                               | —                  | _    | 0.2  | V    |

| Short-circuit protection circuit         | block                 |                                                               |                    |      |      |      |

| Input standby voltage                    | V <sub>STBY</sub>     |                                                               | _                  | —    | 0.1  | V    |

| Input threshold voltage                  | V <sub>THPC</sub>     |                                                               | 0.8                | 0.9  | 1.0  | V    |

| Input latch voltage                      | V <sub>IN</sub>       |                                                               |                    | _    | 0.1  | V    |

| Charge current                           | I <sub>CHG</sub>      | $V_{SCP} = 0 V$                                               | -1.3               | -1.0 | -0.7 | μΑ   |

| Comparator threshold voltage             | V <sub>THL</sub>      |                                                               | _                  | 1.26 | —    | V    |

| On/off control block                     |                       |                                                               |                    |      |      |      |

| Input threshold voltage                  | V <sub>ON(TH)</sub>   |                                                               | 0.7                | 1.0  | 1.3  | V    |

| Off pin current                          | I <sub>OFF</sub>      | $V_{OFF} = 5 V$                                               | _                  | 35   |      | μΑ   |

| CTL block                                |                       |                                                               |                    |      |      |      |

| Input threshold voltage                  | V <sub>THCTL</sub>    |                                                               | 1.07               | 1.26 | 1.47 | V    |

| Charge current                           | I <sub>CTL</sub>      | $V_{CTL} = 0 V$                                               | -1.3               | -1.0 | -0.7 | μΑ   |

| Whole device                             |                       |                                                               |                    |      |      |      |

| Average consumption current              | I <sub>CC(OFF)</sub>  | $R_B = 9.1 \text{ k}\Omega$ , duty = 50%                      |                    | 4.2  | 5.5  | mA   |

| Standby mode current                     | I <sub>CC(SB)</sub>   |                                                               | _                  |      | 1    | μΑ   |

## Terminal Equivalent Circuits

| Pin No. | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I/O |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1       | $\begin{array}{c} 7 (20) (15) \\ 50 \text{ k}\Omega \\ 1 \\ 50 \text{ k}\Omega \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DT2:<br>Sets the channel 2 soft start time.<br>Set the time by connecting a capacitor between<br>this pin and ground.<br>Note that although the channel 2 maximum on<br>duty is set internally to 86%, the maximum on<br>duty can be set to a value of 86% or less by<br>inserting a resistor between this pin and ground,<br>and can be set to a value of 86% or more by inse-<br>rting a resistor between this pin and the V <sub>REF</sub> pin.                                                                                                                                    | Ι   |

| 2       | $\begin{array}{c} \hline 7 & \boxed{22} & \boxed{15} \\ 50 & \mathrm{k\Omega} \\ \hline 2 \\ \hline 50 & \mathrm{k\Omega} \end{array}$ PWM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DT1:<br>Sets the channel 1 soft start time.<br>Set the time by connecting a capacitor between<br>this pin and ground.<br>Note that although the channel 1 maximum on<br>duty is set internally to 86%, the maximum on<br>duty can be set to a value of 86% or less by<br>inserting a resistor between this pin and ground,<br>and can be set to a value of 86% or more by inse-<br>rting a resistor between this pin and the V <sub>REF</sub> pin.                                                                                                                                    |     |

| 3       | $V_{CC}$<br>$20 \text{ k}\Omega$<br>$1.1 \mu\text{A}$<br>1.26 V<br>1.26 V<br>1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CTL3:<br>Controls the on/off state of channel 3.<br>A delay can be provided in the power supply<br>turn-on start time by connecting a capacitor<br>between this pin and ground.<br>$t_{DLY3} = 1.26 \text{ (V)} \times C_{CTL3} (\mu\text{F})/1.1 (\mu\text{A}) \text{ (s)}$<br>This pin can also be used to control the on/off<br>state with an external signal.<br>In that case, the allowable input voltage range is<br>from 0 V to V <sub>CC</sub> . Note that during U.V.L.O. and<br>timer latch operation, this pin is connected to<br>ground through a 20 k $\Omega$ resistor. | Ι   |

| 4       | $V_{CC}$ $20 \text{ k}\Omega$ $1.1 \mu\text{A}$ $1.26 \text{V}$ $1.26 $ | CTL2:<br>Controls the on/off state of channel 2.<br>A delay can be provided in the power supply<br>turn-on start time by connecting a capacitor<br>between this pin and ground.<br>$t_{DLY2} = 1.26 (V) \times C_{CTL2} (\mu F)/1.1 (\mu A)$ (s)<br>This pin can also be used to control the on/off<br>state with an external signal.<br>In that case, the allowable input voltage range is<br>from 0 V to V <sub>CC</sub> . Note that during U.V.L.O. and<br>timer latch operation, this pin is connected to<br>ground through a 20 k $\Omega$ resistor.                             | Ι   |

## Terminal Equivalent Circuits (continued)

| Pin No. | Equivalent circuit                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I/O |

|---------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5       | V <sub>CC</sub><br>$20 \text{ k}\Omega$ $1.1 \mu\text{A}$ High -<br>1.26 V is turned off.<br>5 | CTL1:<br>Controls the on/off state of channel 1.<br>A delay can be provided in the power supply<br>turn-on start time by connecting a capacitor<br>between this pin and ground.<br>$t_{DLY1} = 1.26 \text{ (V)} \times C_{CTL1} (\mu \text{F})/1.1 (\mu \text{A}) \text{ (s)}$<br>This pin can also be used to control the on/off<br>state with an external signal.<br>In that case, the allowable input voltage range is<br>from 0 V to V <sub>CC</sub> . Note that during U.V.L.O. and<br>timer latch operation, this pin is connected to<br>ground through a 20 k $\Omega$ resistor. | Ι   |

| 6       | $ \begin{array}{c}                                     $                                       | Off:<br>Controls the on/off state.<br>When the input is high: normal operation<br>$(V_{OFF} > 1.2 \text{ V})$<br>When the input is low: standby mode<br>$(V_{OFF} < 0.6 \text{ V})$<br>In standby mode, the total current consumption is held to under 1 $\mu$ A.                                                                                                                                                                                                                                                                                                                       | Ι   |

| 7       |                                                                                                | $V_{REF}$ :<br>Outputs the internal reference voltage.<br>The reference voltage is 1.26 V (allowance:<br>$\pm 1\%$ ) when $V_{CC}$ is 2.4 V and $I_{REF}$ is – 0.1 mA.<br>Insert a capacitor of at least 0.1 µF between $V_{REF}$<br>and ground for phase compensation.                                                                                                                                                                                                                                                                                                                 | 0   |

| 8       | $V_{CC}$                                                                                       | RB2:<br>Connection for a resistor that sets the channel 2<br>output source current.<br>Use a resistor in the range 750 $\Omega$ to 1.5 k $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ι   |

| 9       | $V_{CC}$                                                                                       | RB1:<br>Connection for a resistor that sets the channel 1<br>output source current.<br>Use a resistor in the range 750 $\Omega$ to 1.5 k $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ι   |

## Terminal Equivalent Circuits (continued)

| Pin No. | Equivalent circuit                                                                         | Description                                                                                                                                                                                                                                                                                        | I/O |

|---------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10      | V <sub>CC</sub><br>9<br>V <sub>CC</sub><br>V <sub>CC</sub><br>1<br>50(OUT)1<br>10<br>30 kΩ | OUT1:<br>Push-pull output.<br>The absolute maximum rating for the output<br>source current is –50 mA.<br>Connecting the external resistor to RB1 terminal<br>allows this circuit to provide an output source<br>current with excellent line regulation and minimal<br>sample-to-sample variations. | Ο   |

| 11      | V <sub>CC</sub>                                                                            | OUT2:<br>Push-pull output.<br>The absolute maximum rating for the output<br>source current is -50 mA.<br>Connecting the external resistor to RB2 terminal<br>allows this circuit to provide an output source<br>current with excellent line regulation and minimal<br>sample-to-sample variations. | Ο   |

| 12      | (12)                                                                                       | GND:<br>Ground.                                                                                                                                                                                                                                                                                    |     |

| 13      | V <sub>cc</sub>                                                                            | OUT3:<br>Open-collector output.<br>The absolute maximum rating for the output<br>current is +50 mA.                                                                                                                                                                                                | 0   |

| 14      |                                                                                            | V <sub>CC</sub> :<br>Power supply terminal.<br>Provide the operating supply voltage in the range<br>1.8 V to 14 V.                                                                                                                                                                                 |     |

| 15      | $V_{CC}$<br>Latch<br>$0.2 V \frac{S}{R} \overline{Q}$                                      | OSC:<br>Connection for the capacitor and resistor that<br>determine the oscillator frequency. Use a capa-<br>citor in the range 100 pF to 1000 pF and a resistor<br>in the range 3 k $\Omega$ to 33 k $\Omega$ . Use an oscillator<br>frequency in the range 20 kHz to 1 MHz.                      | 0   |

| 16      | V <sub>cc</sub> •                                                                          | IN+3:<br>Noninverting input to the error amplifier 3.                                                                                                                                                                                                                                              | Ι   |

| 17      | $\begin{array}{c} 17 16 \\ 1.5 \text{ k}\Omega \end{array}$                                | IN–3:<br>Inverting input to the error amplifier 3.                                                                                                                                                                                                                                                 | Ι   |

## Terminal Equivalent Circuit (continued)

| Pin No. | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                        | I/O |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 18      | 7<br>31 μA<br>OSC<br>PWM3<br>10.5 mA<br>min.<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FB3:<br>Output from the error amplifier 3.<br>This circuit can provide a source current of $-31$ µA or a sink current of 0.5 mA (minimum).         | Ο   |

| 19      | (19)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IN–2:<br>Inverting input to the error amplifier 2.                                                                                                 | Ι   |

| 20      | $V_{CC}$<br>$31 \mu A$<br>0SC<br>19<br>1.26 V<br>1.26 V<br>1.26 V<br>1.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | FB2:<br>Output from the error amplifier 2.<br>This circuit can provide a source current of $-31$<br>$\mu$ A or a sink current of 0.5 mA (minimum). | 0   |

| 21      | (14) $(21)$ $(13)$ $(21)$ $(13)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ $(14)$ | IN–1:<br>Inverting input to the error amplifier 1.                                                                                                 | Ι   |

| 22      | $V_{CC}$<br>(21)<br>1.26 V<br>(0.5  mA)<br>(22)<br>(22)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FB1:<br>Output from the error amplifier 1.<br>This circuit can provide a source current of $-31$<br>$\mu$ A or a sink current of 0.5 mA (minimum). | 0   |

## Terminal Equivalent Circuits (continued)

| Pin No. | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         | I/O |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 23      | $V_{CC}$ $1.1 \ \mu A$ $1.5 \ k\Omega$ $1.1 \ \mu A$ $1.26 \ V$ $R$ $Output$ $V$ | S.C.P.:<br>Connection for the capacitor that sets the timer<br>latch short-circuit protection circuit time<br>constant. Use a capacitor with a value of 1 000<br>pF or higher.<br>The charge current $I_{CHG}$ is 1.1 µA typical.                                                                                                                                                                                                                   | 0   |

| 24      | 7)(18)(15)<br>50 kΩ<br>24<br>50 kΩ<br>777<br>PWM3<br>777                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DT3:<br>Sets the channel 3 soft start time.<br>Set the time by connecting a capacitor between<br>this pin and ground. Note that although the<br>channel 3 maximum on duty is set internally to<br>86%, the maximum on duty can be set to a value<br>of $86\%$ or less by inserting a resistor between<br>this pin and ground, and can be set to a value of<br>86% or more by inserting a resistor between this<br>pin and the V <sub>REF</sub> pin. | Ι   |

#### Usage Notes

#### [1] Allowable power dissipation

Since the power dissipation (P) in this IC increases proportionally with the supply voltage, applications must be careful to operate so that the loss does not exceed the allowable power dissipation,  $P_D$ , for the package.

Reference formula:

| $+ (V_{CC} - V_{E})$      | $I_{BEQ2} \times I_{SO(OUT)2} \times Du_2$ $\langle I_{OUT3} \times Du_3$            | <ul> <li>← Power dissipation in the channel 1 output stage</li> <li>← Power dissipation in the channel 2 output stage</li> <li>← Power dissipation in the channel 3 output stage</li> <li>← Power dissipation between V<sub>CC</sub> and ground</li> </ul> |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| < P <sub>D</sub>          |                                                                                      |                                                                                                                                                                                                                                                            |  |  |  |

| V <sub>BEQ1</sub> : T     | The voltage between the ba                                                           | se and emitter of the npn transistor Q1                                                                                                                                                                                                                    |  |  |  |

| $I_{SO(OUT)1}$ : 7        | The OUT1 pin output sourc                                                            | ce current                                                                                                                                                                                                                                                 |  |  |  |

| C                         | When $R_{RB1}$ is 1 k $\Omega$ , $I_{SO(OU)}$                                        | <sub>T)1</sub> will be 38 mA, maximum.)                                                                                                                                                                                                                    |  |  |  |

| Du <sub>1</sub> : 7       | : The output 1 duty factor                                                           |                                                                                                                                                                                                                                                            |  |  |  |

| V <sub>BEQ2</sub> : T     | : The voltage between the base and emitter of the npn transistor Q2                  |                                                                                                                                                                                                                                                            |  |  |  |

| I <sub>SO(OUT)2</sub> : T | The OUT2 pin output sourc                                                            | ce current                                                                                                                                                                                                                                                 |  |  |  |

| C                         | When $R_{RB2}$ is 1 k $\Omega$ , $I_{SO(OU)}$                                        | <sub>T)2</sub> will be 38 mA, maximum.)                                                                                                                                                                                                                    |  |  |  |

| Du <sub>2</sub> : 7       | The output 2 duty factor                                                             |                                                                                                                                                                                                                                                            |  |  |  |

| V <sub>O(SAT)3</sub> : 7  | The OUT3 pin saturation vo                                                           | oltage (0.5 V maximum when OUT1 is 40 mA.)                                                                                                                                                                                                                 |  |  |  |

| I <sub>OUT3</sub> : T     | : The OUT3 pin current (This will be $\{V_{CC} - V_{BEQ3} - V_{O(SAT)3}\}/R_{O3}$ .) |                                                                                                                                                                                                                                                            |  |  |  |

| Du <sub>3</sub> : 7       | The output 3 duty factor                                                             |                                                                                                                                                                                                                                                            |  |  |  |

| I <sub>CC</sub> : 1       | The V <sub>CC</sub> pin current                                                      |                                                                                                                                                                                                                                                            |  |  |  |

#### ■ Usage Notes (continued)

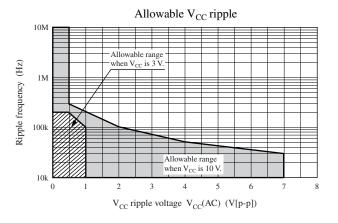

#### [2] Allowable V<sub>CC</sub> ripple

$V_{CC}$  ripple due to the switching transistor being turned on and off can cause this IC's U.V.L.O. circuit, which is biased by  $V_{CC}$ , to operate incorrectly, and can cause the S.C.P. capacitor charging operation to fail to start when the output is shorted.

The figure shows the allowable range for  $V_{CC}$  ripple. Applications should reduce  $V_{CC}$  ripple to be within this range, either by inserting a ripple filter in the  $V_{CC}$  line or by inserting a capacitor between the IC GND and  $V_{CC}$  pins and locating that capacitor as close to the IC as possible.

Note that the allowable range shown here is the result of testing the IC alone and that the allowable range may differ depending on the actual structure of the power supply circuit. Also note that this allowable range is a design target, and is not guaranteed by testing of all samples.

#### Application Notes

#### [2] Main characteristics

Timing capacitance - Oscillator frequency

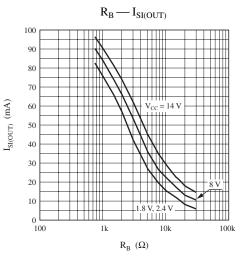

[3] Timing charts

#### [4] Function descriptions

#### 1. Reference voltage block

This circuit is composed of a band gap circuit, and outputs a 1.26 V (typical) reference voltage that is temperature compensated to a precision of  $\pm 1\%$ . This reference voltage is stabilized when the supply voltage is 1.8 V or higher. This reference voltage is used by error amplifiers 1 and 2.

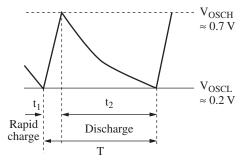

2. Triangular wave generator

This circuit generates a triangular wave like a sawtooth with a peak of 0.7 V and a trough of 0.2 V using a capacitor  $C_T$  (for the time constant) and resistor  $R_T$  connected to the OSC pin (pin 15). The oscillator frequency can be set to an arbitrary value by selecting appropriate values for the external capacitor and resistor,  $C_T$  and  $R_T$ . This IC can use an oscillator frequency in the range 20 kHz to 1 MHz. The triangular wave signal is provided to the noninverting input of the PWM comparator in each channel internally to the IC. Use the formulas below for rough calculation of the oscillator frequency.

Figure 1. Triangular oscillator waveform

Note, however, that the above formulas do not take the rapid charge time, overshoot, and undershoot into account. See the experimentally determined graph of the oscillator frequency vs. timing capacitance value provided in the main characteristics section.

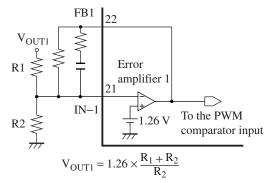

3. Error amplifier 1

This circuit is an npn-transistor input error amplifier that detects and amplifies the DC-DC converter output voltage, and inputs that signal to a PWM comparator. The 1.26 V internal reference voltage is applied to the noninverting input. Arbitrary gain and phase compensation can be set up by inserting a resistor and capacitor in series between the FB1 pin (pin 22) and the IN–1 pin (pin 21). The output voltage  $V_{OUT1}$  can be set using the circuit shown in the figure.

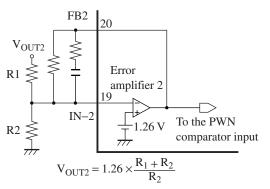

4. Error amplifier 2

This circuit is an npn-transistor input error amplifier that detects and amplifies the DC-DC converter output voltage, and inputs that signal to a PWM comparator. The 1.26 V internal reference voltage is applied to the noninverting input. Arbitrary gain and phase compensation can be set up by inserting a resistor and capacitor in series between the FB2 pin (pin 20) and the IN–2 pin (pin 19). The output voltage  $V_{OUT2}$  can be set using the circuit shown in the figure.

Figure 2. Connection method of error amplifier 1 (Step-up output)

- [4] Function descriptions (continued)

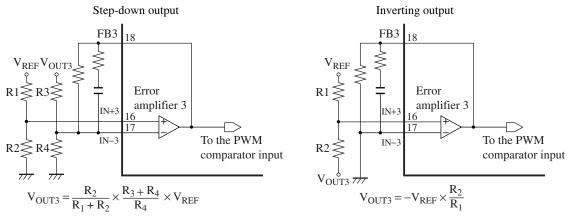

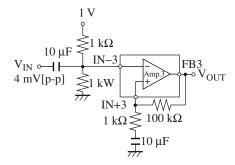

- 5. Error amplifier 3

This circuit is a pnp-transistor input error amplifier that detects and amplifies the DC-DC converter output voltage and inputs that signal to a PWM comparator. Arbitrary gain and phase compensation can be set up by inserting a resistor and capacitor in series between the FB3 pin (pin 18) and the IN-3 pin (pin 17). The output voltage  $V_{OUT3}$  can be set using the circuit shown in the figure.

Figure 4. Connection method of error amplifier 3

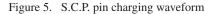

#### 6. Timer latch short-circuit protection circuit

This circuit protects the external main switching elements, flywheel diodes, choke coils, and other components against degradation or destruction if an excessive load or a short circuit of the power supply output continues for longer than a certain fixed period.

The timer latch short-circuit protection circuit detects the output of the error amplifiers. If the DC-DC converter output voltage drops and an FB pin (pins 18, 20, or 22) voltage exceeds 0.9 V, the S.C.P. comparator outputs a low level and the timer circuit starts. This starts charging the external protection circuit delay time capacitor.

If the error amplifier output does not return to the normal voltage range before that capacitor reaches 1.26 V, the latch circuit latches, the output drive transistors are turned off, and the dead-time is set to 100%.

#### 7. Low input voltage malfunction prevention circuit (U.V.L.O.)

This circuit protects the system against degradation or destruction due to incorrect control operation when the power supply voltage falls during power on or power off.

The low input voltage malfunction prevention circuit detects the internal reference voltage that changes with the supply voltage level. While the supply voltage is rising, this circuit cuts off the output drive transistor until the reference voltage reaches 1.67 V. It also sets the dead-time to 100% and at the same time holds the S.C.P. pin (pin 23) and the DT pins (pins 1, 2, and 24) at 0 V, and the OSC pin (pin 15) at about 1.2 V.

8. PWM comparators

The PWM comparators control the on-period of the output pulse according to their input voltage.

The output transistors are turned on during periods when the OSC pin (pin 15) triangular wave is lower than both of the corresponding FB pin (pins 18, 20, or 22) and the corresponding DT pin (pins 1, 2, or 24).

The PWM 2 circuit turns the output transistor on during periods when OSC pin (pin 15) triangular wave is at a higher level than both of the FB2 pin (pin 20) and the DT2 pin (pin 1).

The maximum duty is set to 86% internally, but it can be set to a value lower than 86% by inserting a resistor between the corresponding DT pin and ground, and can be set to a value higher than 86% by inserting a resistor between the corresponding DT pin and the  $V_{REF}$  pin.

The IC's soft start function operates to gradually increase the width of the output pulse on-period during startup if a capacitor is inserted between the DT pin and ground.

#### [4] Function descriptions (continued)

9. Output 1 and output 2 blocks

These output circuits have a totem pole structure. A constant-current source output with good line regulation can be set up freely by connecting current setting resistors to the RB pins.

These circuits can provide a constant-current source output of up to 50 mA.

10. Output 3 block

This output circuit has an open collector structure.

An output current of up to 50 mA can be provided, and the output pin has a breakdown voltage of 15 V.

11. CTL block

The CTL block output circuit also has a totem pole structure. A constant-current source output with good line regulation can be set up freely by connecting current setting resistors to the RB2 pin.

The CTL block can provide a constant-current source output of up to 50 mA.

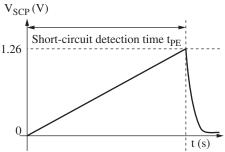

#### [5] Time constant setup for the timer latch short-circuit protection circuit

Figure 6 shows the structure of the timer latch short-circuit protection circuit. The short-circuit protection comparator continuously compares a 0.9 V reference voltage with the FB1, FB2, and FB3 error amplifier outputs.

When the DC-DC converter output load conditions are stable, the short-circuit protection comparator holds its average value since there are no fluctuations in the error amplifier outputs. At this time, the output transistor Q1 will be in the conducting state, and the S.C.P. pin will be held at 0 V.

If the output load conditions change rapidly and a high-level signal (0.9 V or higher) is input to the short-circuit protection comparator from the error amplifier output, the short-circuit protection comparator will output a low level and the output transistor Q1 will shut off. Then, the capacitor  $C_{SCP}$  connected to the S.C.P. pin will start to charge. When the external capacitor  $C_{SCP}$  is charged to about 1.26 V by the constant current of about 1.1 mA, the latch circuit will latch and the dead-time will be set to 100% with the output held fixed at the low level. Once the latch circuit has latched, the S.C.P. pin capacitor will be discharged to about 0 V, but the latch circuit will not reset unless either power is turned off or the power supply is restarted using on/off control.

$$1.26 \text{ V} = \text{I}_{\text{CHG}} \times \frac{\text{t}_{\text{PE}}}{\text{C}_{\text{SCP}}}$$

$$\therefore \text{ t}_{\text{PE}} (s) = 1.15 \times \text{C}_{\text{SCP}} (\mu\text{F})$$

At power supply startup, the output appears to be in the shorted state, and the IC starts to charge the S.C.P. pin capacitor. Therefore, users must select an external capacitor that allows the DC-DC converter output voltage to rise before the latch circuit in the later stage latches. In particular, care is required if the soft start function is used, since that function makes the startup time longer.

Figure 6. Short-circuit protection circuit

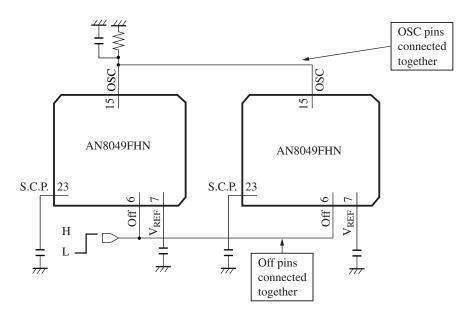

#### [6] Parallel synchronous operation of multiple ICs

Multiple instances of this IC can be operated in parallel. If the OSC pins (pin 15) and Off pins (pin 6) are connected to each other as shown in figure 7, the ICs will operate at the same frequency.

It is also possible to operate a one-channel control IC (e.g. the AN8016SH or AN8016NSH) and a two-channel control IC (e.g. the AN8017SA or AN8018SA) in this parallel synchronous mode. In this case, short the OSC and Off pins together.

Note that it is not possible to control the on/off states of each IC operating in this mode independently. It is only possible to turn all the ICs on or off at the same time remotely.

Figure 7. Slave operation circuit example

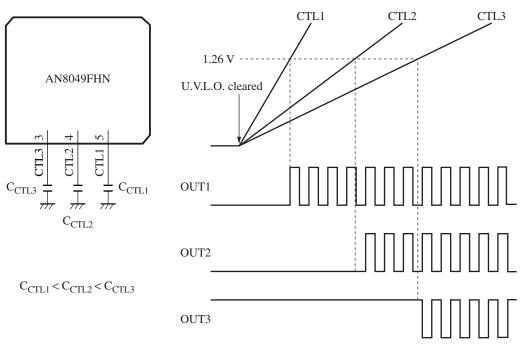

#### [7] Sequential operation

Delays can be provided in the startup times by inserting capacitors ( $C_{CTL}$ ) between the CTL pins and ground. Delay time:  $t_{DLY} = 1.26$  (V) ×  $C_{CTL}$  ( $\mu$ F)/1.1 ( $\mu$ A) (s)

Note that the individual channels can also be turned on or off independently by external signals. These external signals may have voltages in the range 0 V to  $V_{CC}$ .

Figure 8. Sequential operation

[8] Differences between this IC and the AN8049SH The pin arrangements differ. The AN8049SH is an alternative package version of this IC.

#### AN8049FHN

AN8049SH OUT2

22

FB2

21

IN-2

20

FB3

19

IN-3

19

IN-3

11

OSC

OUT3 GND IN-1  $\mathbf{v}_{\mathrm{cc}}$ FB1 24 23 16 14 13 1012 11  $\infty$ 6 2 S.C.P. DT3 DT2 CTL3 CTL2 CTL1 Off VREF RB2 DT1 **OUT1** RB1

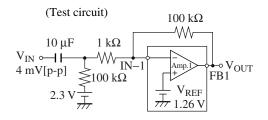

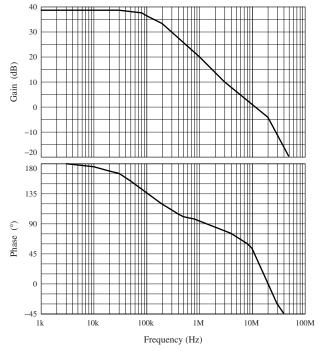

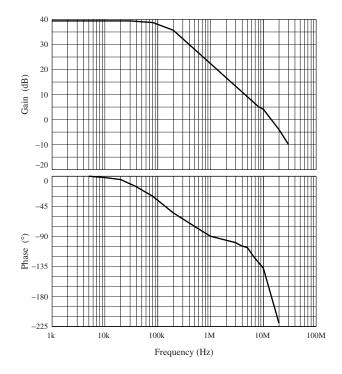

- [9] Error amplifier frequency characteristics

- 1. Error amplifiers 1 and 2

2. Error amplifier 3

(Test circuit)

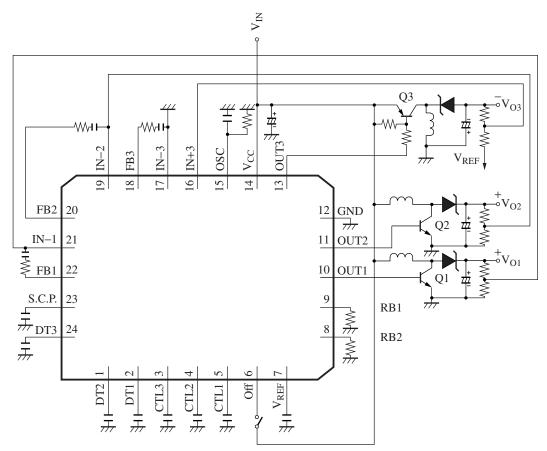

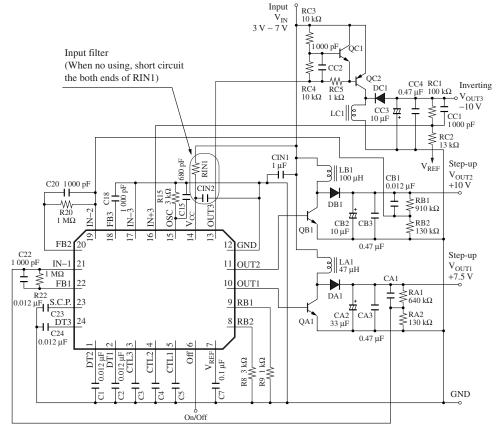

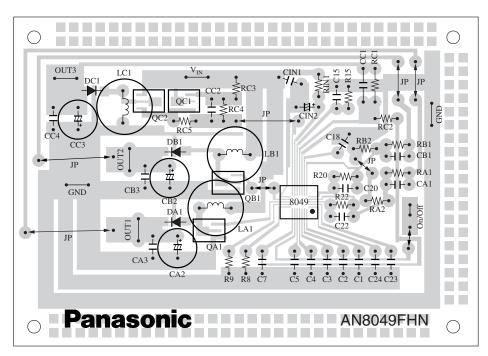

## ■ Application Circuit Example

#### Evaluation Board

- 1. The element numbers of the board pair with the ones of the circuit.

- 2. "JP" of the board shows the jumper. Short circuit.

- Circuit

Board

## Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuit examples of the products. It does not constitute the warranting of industrial property, the granting of relative rights, or the granting of any license.

- (3) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this material are subject to change without notice for reasons of modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, redundant design is recommended, so that such equipment may not violate relevant laws or regulations because of the function of our products.